# Fundamentos dos circuitos sequenciais

A grande maioria das aplicações dos sistemas digitais requer a capacidade de memória, isto é, a capacidade de armazenar informação digital binária. Por exemplo, um simples sistema de controlo digital para a abertura de uma porta tem necessidade de armazenar o código binário das teclas sucessivamente digitadas num teclado. De facto, a aplicabilidade dos sistemas digitais seria extremamente reduzida se se limitasse à utilização de circuitos combinacionais.

# Dispositivo de memória digital binária

Um dispositivo de memória digital binária, também designado por célula de memória, deve permitir:

- a operação de escrita, ou seja, armazenar o valor lógico 0 ou 1 (bit);

- a operação de leitura do valor previamente armazenado, mantendo inalterado esse valor até que uma nova operação de escrita ocorra.

## Construção de dispositivos de memória

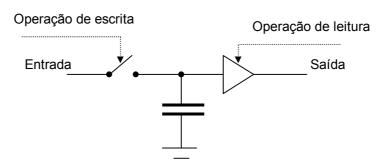

Utilização de mecanismos de armazenamento analógico.

Quando se pretende armazenar um valor lógico, o comutador de entrada é fechado durante o tempo necessário para carregar o condensador à tensão aplicada na entrada (escrita do valor lógico 0 ou 1). O buffer, existente na saída, permite que, quando activo (operação de leitura), a saída reproduza a tensão do condensador sem lhe retirar ou acrescentar carga (isolamento eléctrico). Este é o modo de operação ideal. No entanto, devido a percursos de fuga, o condensador tende a perder carga, sendo, por isso, necessária a actualização periódica da tensão no condensador. Os dispositivos de memória baseados nesta tecnologia têm um circuito interno temporizado responsável pelo "refrescamento", isto é, restabelece a tensão do condensador para os níveis admissíveis na representação dos valores lógicos armazenados. Devido à complexidade destes circuitos, este tipo de tecnologia é preferencialmente utilizado em sistemas de elevada capacidade de armazenamento, tipicamente, a memória principal dos sistemas computacionais.

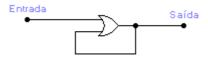

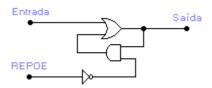

Utilização de portas lógicas (circuitos combinacionais) com realimentação de sinais das saídas para as entradas.

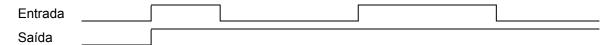

#### Descrição funcional

Supondo que o estado inicial da saída é 0, enquanto a entrada se mantiver a 0, a saída não sofre alteração de estado. A partir do instante em que a entrada passa ao estado 1, a saída transita para o estado 1, mantendo este estado indefinidamente. Este circuito apresenta capacidade de memória pois memoriza a ocorrência do primeiro 1 que seja colocado na entrada.

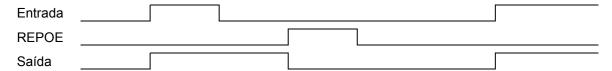

### Diagrama temporal

O circuito anterior pode ser alterado de modo a permitir colocar a saída no estado 0. A entrada adicional REPOE, quando activa, permite colocar a saída no estado 0 (excepto se nesse momento a entrada estiver a 1).

### Diagrama temporal

Este circuito implementa a função básica de uma célula de memória pois, por um lado, é possível "ler" a saída sem alterar o seu valor e, por outro, permite a operação de escrita de um dos valores lógicos 0 ou 1.

# Circuitos sequenciais e circuitos combinacionais

#### Circuitos combinacionais

- As saídas dependem apenas do estado presente das entradas.

- Exemplos: portas lógicas, multiplexers, descodificadores, etc.

# Circuitos sequenciais

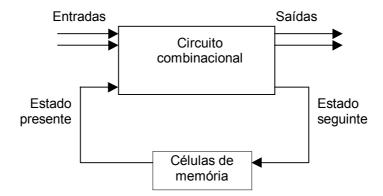

- As saídas dependem, não só do estado actual das entradas, mas também da sequência de estados aplicada nas entradas.

- São constituídos, para além de outros elementos combinacionais, por células de memória que armazenam o estado presente do sistema que define, em conjunto com as entradas, o comportamento futuro das saídas e do próprio estado do sistema.

- Exemplos: básculas, "flip-flops", máquinas de estado, contadores, registos de dados, registos de deslocamento, etc.

#### Estrutura geral de um circuito sequencial

## Circuitos seguenciais assíncronos e síncronos

## Circuitos sequenciais assíncronos

A memória (que determina o estado presente de um circuito) é constituída por um conjunto de células de memória assíncronas, isto é, que reagem de imediato a qualquer alteração que se verifique nas entradas.

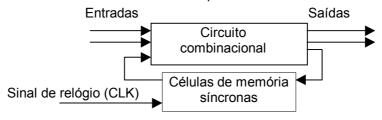

# Circuitos sequenciais síncronos

A memória (que determina o estado presente de um circuito) é constituída por um conjunto de células de memória síncronas, isto é, que reagem de forma sincronizado com um sinal, designado por sinal de relógio ("Clock"-CLK), que determina o instante em que se verifica alteração de estado num sistema.

#### Circuito sequencial síncrono

### Características do sinal de relógio

Define o instante em que se verifica a alteração de estado num circuito sequencial síncrono.

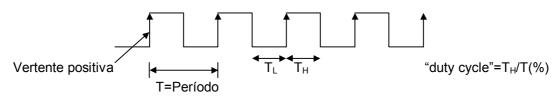

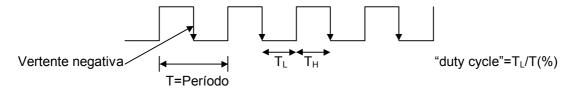

Período: Intervalo de tempo entre duas transições no mesmo sentido.

Frequência: inverso do período.

"duty cycle": percentagem de tempo, relativamente ao período, em que o sinal de relógio está activo. Nível de activação:

- Activo ao nível alto as células de memória reagem à vertente positiva do sinal, ou seja, quando se dá a transição do estado baixo para o estado alto.

- Activo ao nível baixo as células de memória reagem à vertente negativa do sinal, ou seja, quando se dá a transição do estado alto para o estado baixo.

#### Sinal de relógio activo ao nível alto

Frequência=1/T=1/Período

Sinal de relógio activo ao nível baixo

## Células de memória assíncronas

Neste tipo de células, qualquer alteração de estado nas entradas provoca, de imediato ( a menos do tempo de propagação das portas lógicas), alteração no estado das saídas.

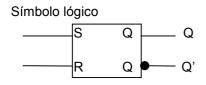

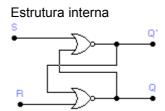

## Báscula S-R / "S-R Latch"

Funcionamento básico: A entrada S ("Set") permite colocar a saída Q a 1 e a entrada R("Reset") permite colocar a saída a 0.

| Estado presente(N) | Condições de entrada | Estado seguinte(N+1) | Descrição                    |

|--------------------|----------------------|----------------------|------------------------------|

| Q=0, Q'=1          | S=0, R=0             | Q=0, Q'=1            | Mantém-se o estado anterior  |

| Q=1, Q'=0          | S=0, R=0             | Q=1, Q'=0            | Mantém-se o estado anterior  |

| Q=0, Q'=1          | S= 0 _ 1 , R=0       | Q=1, Q'=0            | Coloca a saída a 1 ("Set")   |

| Q=1, Q'=0          | S= 0 _ 1 , R=0       | Q=1, Q'=0            | Coloca a saída a 1 ("Set")   |

| Q=0, Q'=1          | S= 0, R=0_ 1         | Q=0, Q'=1            | Coloca a saída a 0 ("Reset") |

| Q=1, Q'=0          | S= 0, R=0 [1         | Q=0, Q'=1            | Coloca a saída a 0 ("Reset") |

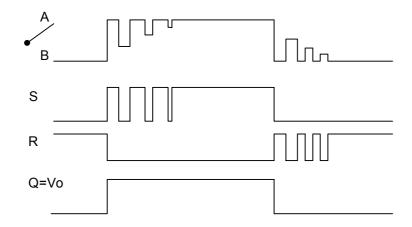

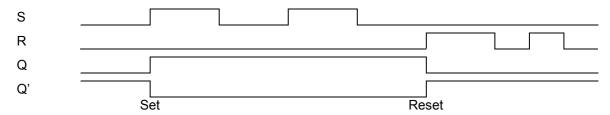

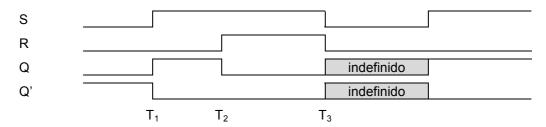

# Diagrama temporal

O que acontece quando, simultaneamente, S=1 e R=1 (instante  $T_2$ )? Ambas a saídas, Q e Q' estão a 0, o que já de si é incongruente, pois estas saídas devem assumir sempre valores complementares. Mais grave é o facto de ser indefinido o estado da saída se simultaneamente( instante  $T_3$ ) ambas as entradas são colocadas a 0. Devido a este comportamento indeterminado, as entradas S e R nunca devem estar activas simultaneamente.

### Tabela funcional

| S | R | $Q_{N+1}$  | •     |

|---|---|------------|-------|

| 0 | 0 | $Q_N$      | •     |

| 0 | 1 | 0          | Reset |

| 1 | 0 | 1          | Set   |

| 1 | 1 | Indefinido |       |

Na tabela funcional,  $Q_N$  representa o estado presente e  $Q_{N+1}$  representa o estado seguinte.

Tabela de excitação

| $Q_N \Rightarrow Q_{N+1}$ | S | R |

|---------------------------|---|---|

| 0⇒0                       | 0 | Χ |

| 0⇒1                       | 1 | 0 |

| 1⇒0                       | 0 | 1 |

| 1⇒1                       | Χ | 0 |

A tabela de excitação define quais os valores a aplicar nas entradas S e R para que determinada transição de estado ocorra na saída (X = condição indiferente).

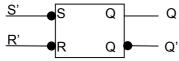

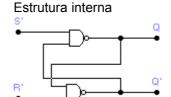

# Báscula S'-R'/ "S'-R' Latch"

Funcionamento básico: O funcionamento é em tudo idêntico à báscula S-R, mas apresenta as entradas activas a 0. A entrada S' ("Set") permite colocar a saída Q a 1 e a entrada R' ("Reset") permite colocar a saída a 0.

| Estado presente(N) | Condições de entrada    | Estado seguinte(N+1) | Descrição                    |

|--------------------|-------------------------|----------------------|------------------------------|

| Q=0, Q'=1          | S'=1, R'=1              | Q=0, Q'=1            | Mantém-se o estado anterior  |

| Q=1, Q'=0          | S'=1, R'=1              | Q=1, Q'=0            | Mantém-se o estado anterior  |

| Q=0, Q'=1          | S'= 1 <u>]</u> 0 , R'=1 | Q=1, Q'=0            | Coloca a saída a 1 ("Set")   |

| Q=1, Q'=0          | S'= 1 <u></u> 0 , R'=1  | Q=1, Q'=0            | Coloca a saída a 1 ("Set")   |

| Q=0, Q'=1          | S'= 1, R'=1 <u>0</u>    | Q=0, Q'=1            | Coloca a saída a 0 ("Reset") |

| Q=1, Q'=0          | S'= 1, R'=1]_0          | Q=0, Q'=1            | Coloca a saída a 0 ("Reset") |

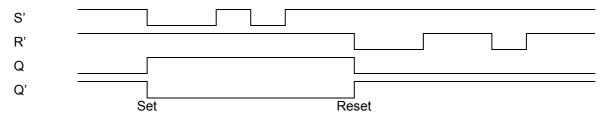

#### Diagrama temporal

Tal como acontece com a báscula S-R, as duas entradas S' e R' nunca devem estar simultaneamente activas, ou seja, S'=R'=0.

#### Tabela funcional

| S' | R' | $Q_{N+1}$  |       |

|----|----|------------|-------|

| 0  | 0  | Indefinido |       |

| 0  | 1  | 1          | Set   |

| 1  | 0  | 0          | Reset |

| 1  | 1  | $Q_N$      |       |

Na tabela funcional,  $Q_N$  representa o estado presente e  $Q_{N+1}$  representa o estado seguinte.

Tabela de excitação

| agao                      |   |   |  |

|---------------------------|---|---|--|

| $Q_N \Rightarrow Q_{N+1}$ | ŝ | Ř |  |

| 0⇒0                       | 1 | Χ |  |

| 0⇒1                       | 0 | 1 |  |

| 1⇒0                       | 1 | 0 |  |

| 1⇒1                       | Χ | 1 |  |

A tabela de excitação define quais os valores a aplicar nas entradas S' e R' para que determinada transição de estado ocorra na saída (X = condição indiferente).

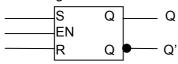

# Báscula S-R porteada/ "S-R Latch with enable"

De acordo com a tabela funcional de uma báscula S-R, as entradas a 0 não afectam as saídas. Assim sendo, é possível controlar a sensibilidade da báscula através de uma entrada adicional de "enable" (EN).

Funcionamento básico: O funcionamento é em tudo idêntico à báscula S-R, mas esta só é sensível a alterações nas entradas apenas enquanto a entrada de enable estiver activa (EN=1).

#### Tabela funcional

| ΕN | S | R | $Q_{N+1}$  |       |

|----|---|---|------------|-------|

| 1  | 0 | 0 | $Q_N$      |       |

| 1  | 0 | 1 | 0          | Reset |

| 1  | 1 | 0 | 1          | Set   |

| 1  | 1 | 1 | Indefinido |       |

| 0  | Χ | Χ | $Q_N$      | _     |

|    |   |   |            |       |

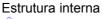

# Báscula D / "D Latch – transparent latch"

Este tipo de célula de memória assíncrona tem por base uma báscula S-R porteada, cujas entradas estão ligadas a uma única entrada D. Quando a entrada de enable está activa, a saída reflecte, de forma transparente, a informação binária colocada na entrada D.

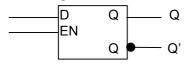

## Símbolo lógico

### Estrutura interna

#### Tabela funcional

| EN | D | Q     |

|----|---|-------|

| 1  | 0 | 0     |

| 1  | 1 | 1     |

| 0  | Χ | $Q_N$ |

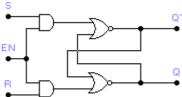

## Exemplo de aplicação de uma báscula S-R

Um exemplo de aplicação deste circuito é a filtragem do ruído introduzido pelo comutadores mecânicos.

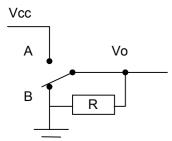

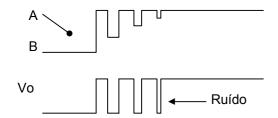

♦ Comutador com ruído

A função da resistência R do circuito é colocar a saída Vo a 0 (valor lógico) sempre que o comutador não efectua o contacto nem com o ponto A nem com o ponto B. Devido ao efeito de mola dos comutadores mecânicos, a transição do comutador de B para A produz ruído na saída Vo, conforme se pode verificar no diagrama temporal.

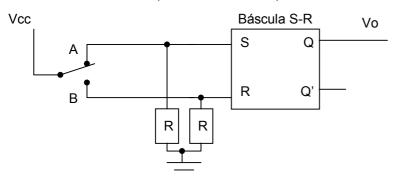

♦ Comutador sem ruído ("debounced switch")

As resistências do circuito colocam as entradas S e R a 0 (valor lógico) sempre que o comutador não efectua o contacto nem com o ponto A nem com o ponto B. Quando o comutador está em contacto com o ponto B, S=0 e R=1, estando a saída Vo=Q a 0. Na transição do comutador de B para A, R=0 e S vai oscilando entre 1 e 0 até se fixar no valor 1. A primeira ocorrência de S=1 é de imediato capturada pela báscula S-R colocando a saída a 1 (Set). Na transição de A para B, S=0 e R vai oscilando entre 1 e 0 até se fixar no valor 1. A primeira ocorrência de R=1 é de imediato capturada pela báscula S-R, colocando a saída a 0(Reset). Tal como se evidencia no diagrama temporal, a aplicação da báscula S-R neste circuito elimina o ruído eléctrico.

#### Diagrama temporal