#### Trabalho Prático Nº 1

#### Detector de paridade

#### 1-Introdução

Pretende-se construir um circuito que permita verificar se um conjunto de 3 bits tem paridade par (número par de uns)

A função de saída deverá, em princípio, ser implementada na forma mínima soma de produtos. No entanto, deverá verificar se a forma mínima produto de somas conduz a uma implementação mais simples.

A implementação será feita assumindo que se dispõe de portas AND de 2 entradas (IC 7408), portas OR de 2 entradas (IC 7432) e portas NOT (IC7404)

#### 2-Execução do trabalho

- a)-Construa a tabela de verdade

- b)-Preencha o mapa de karnaugh

- c)-Obtenha a função na forma mínima soma de produtos

- d)-Obtenha a função na forma mínima produto de somas.

- e)-Desenhe o diagrama lógico para a implementação atendendo às portas lógicas disponíveis.

- f)-Montagem e teste: Efectue a montagem do circuito e realize o teste, utilizando os comutadores para fornecer as entradas e visualize a função de saída nos LED's, de modo a verificar a tabela de verdade.

- 3-Determine uma implementação que utilize apenas um tipo de porta lógica e indique o tipo de circuito integrado que deveria ser utilizado.

# **7404**

#### Hex inverters.

| ++  |   |         |     | +*+       | _      |

|-----|---|---------|-----|-----------|--------|

| 1A  | 1 | ++ 14   | VCC | A  /Y     | /Y = A |

| /1Y | 2 | 13      | 6A  | +===*===+ |        |

| 2A  | 3 | 12      | /6Y | 0   1     |        |

| /2Y | 4 | 7404 11 | 5A  | 1 0       |        |

| 3A  | 5 | 10      | /5Y | +*+       |        |

| /3Y | 6 | 9       | 4A  |           |        |

| GND | 7 | 8       | /4Y |           |        |

|     | + | +       |     |           |        |

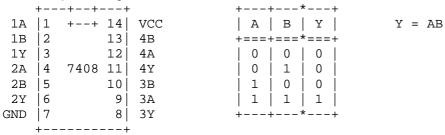

### **7408**

### Quad 2-input AND gates.

# 7432

## Quad 2-input OR gates.

| add 2 mpdt Oft gatos. |   |         |     |                     |  |  |  |  |

|-----------------------|---|---------|-----|---------------------|--|--|--|--|

| ++                    |   |         |     | ++                  |  |  |  |  |

| 1A                    | 1 | ++ 14   | VCC | A   B   Y   Y = A+B |  |  |  |  |

| 1B                    | 2 | 13      | 4B  | +===+===*===+       |  |  |  |  |

| 1Y                    | 3 | 12      | 4A  | 0   0   0           |  |  |  |  |

| 2A                    | 4 | 7432 11 | 4Y  | 0   1   1           |  |  |  |  |

| 2B                    | 5 | 10      | 3B  |                     |  |  |  |  |

| 2Y                    | 6 | 9       | 3A  | 1   1   1           |  |  |  |  |

| GND                   | 7 | 8       | 3Y  | ++                  |  |  |  |  |

| _                     |   |         | _   |                     |  |  |  |  |