#### Trabalho Prático Nº 7

#### Contadores em anel

#### 1. Introdução

Os contadores em anel apresentam um padrão circulante constante (contadores "standard") ou que passa por uma negação no extremo do contador (contadores "twisted").

Sequência de estados (ABCD)

Standard 1000 0100 0010 0001 1000 ....

Twisted 1000 1100 1110 1111 0111 0011 0001 0000 1000 ...

A implementação de contadores deste tipo deve sempre garantir auto-correcção, isto é, qualquer que seja o estado inicial, os contadores devem entrar na sequência principal depois de um número finito de impulsos de relógio.

#### 2. Trabalho a executar

- 2.1 Implemente um contador em anel standard de 4 bits com auto-correcção. Utilize flip-flops do tipo D (IC 74LS74) e portas NOR de duas entradas (IC 74LS02) para a lógica combinacional do circuito de auto-correcção. Utilizando as entradas PRESET e CLEAR, inicialize o contador no estado 1111 e 1011 e verifique se o comportamento do circuito está de acordo com o diagrama de estados (auto-correcção).

- 2.2 Implemente um contador em anel twisted de 4 bits com auto-correcção. Utilize o registo de deslocamento de 4 bits (IC 74LS194) e portas NOR de duas entradas (IC 74LS02) para a lógica combinacional do circuito de auto-correcção. Utilizando as entradas em paralelo do IC 74LS194, inicialize o contador em estados que não pertençam à sequência principal e verifique se o comportamento do circuito está de acordo com o diagrama de estados (auto-correcção).

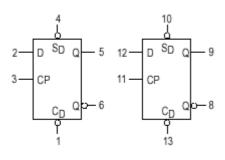

### 7474

# Dual D-Type Positive Edge-Triggered Flip-Flop LOGIC SYMBOL

V<sub>CC</sub> = PIN 14 GND = PIN 7

#### MODE SELECT — TRUTH TABLE

| OPERATING MODE   |                | INPUTS | OUTPUTS |   |   |

|------------------|----------------|--------|---------|---|---|

| OPERATING MODE   | s <sub>D</sub> | СД     | D       | ø | σ |

| Set              | L              | Н      | Х       | Н | L |

| Reset (Clear)    | Н              | L      | Х       | L | Н |

| *Undetermined    | L              | L      | Х       | Н | Н |

| Load "1" (Set)   | Н              | Н      | h       | Н | L |

| Load "0" (Reset) | Н              | Н      | I       | L | Н |

<sup>\*</sup> Both outputs will be HIGH while both S<sub>D</sub> and C<sub>D</sub> are LOW, but the output states are unpredictable if S<sub>D</sub> and C<sub>D</sub> go HIGH simultaneously. If the levels at the set and clear are near V<sub>IL</sub> maximum then we cannot guarantee to meet the minimum level for V<sub>OH</sub>.

H, h = HIGH Voltage Level

L, I = LOW Voltage Level

X = Don't Care

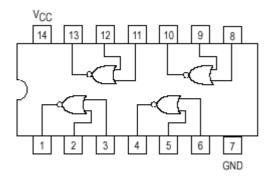

# 7402

#### Quad 2 input NOR

i, h (q) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH to LOW clock transition.

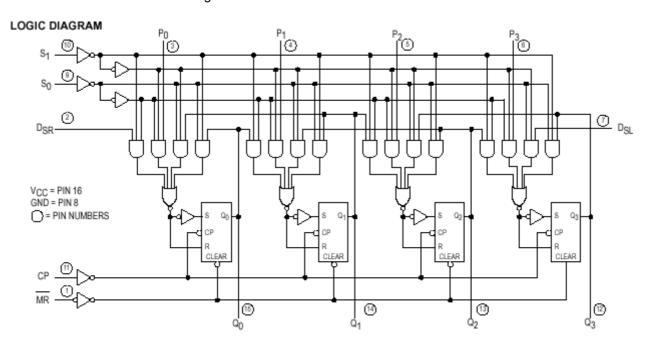

# 74194

# 4 Bits bi-directional Universal Shift Register

#### MODE SELECT — TRUTH TABLE

| OPERATING MODE |    | INPUTS         |                |                 |                 |        | OUTPUTS        |                                  |                |                |  |

|----------------|----|----------------|----------------|-----------------|-----------------|--------|----------------|----------------------------------|----------------|----------------|--|

|                | MR | s <sub>1</sub> | s <sub>0</sub> | D <sub>SR</sub> | D <sub>SL</sub> | Pn     | $Q_0$          | $Q_1$                            | $Q_2$          | $Q_3$          |  |

| Reset          | L  | X              | X              | Х               | Х               | Х      | L              | ┙                                | L              | L              |  |

| Hold           | Н  | I              | - 1            | Х               | Х               | Х      | 90             | q <sub>1</sub>                   | q <sub>2</sub> | <b>q</b> 3     |  |

| Shift Left     | Н  | h<br>h         |                | X<br>X          | l<br>h          | X<br>X | 91<br>91       | q <sub>2</sub><br>q <sub>2</sub> | 93<br>93       | L H            |  |

| Shift Right    | н  | I              | h h            | l<br>h          | X<br>X          | X<br>X | Η              | g0<br>0P                         | 91<br>91       | 92<br>92       |  |

| Parallel Load  | Н  | h              | h              | Х               | Х               | Pn     | P <sub>0</sub> | P <sub>1</sub>                   | P <sub>2</sub> | P <sub>3</sub> |  |

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don't Care

I = LOW voltage level one set-up time prior to the LOW to HIGH clock transition

h = HIGH voltage level one set-up time prior to the LOW to HIGH clock transition

p<sub>n</sub> (q<sub>n</sub>) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to HIGH clock transition.