# Portas lógicas

Para além das portas lógicas elementares (AND, OR e NOT) existem outros tipos de portas e simbologias alternativas.

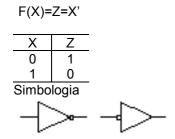

## ♦ Porta NOT (Inversor)

#### ♦ Buffer

Utilizada para amplificar o sinal eléctrico F(X)=Z=X

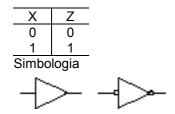

#### ♦ Porta AND

$F(X,Y)=Z=X \cdot Y=(X.Y)''=(X'+Y')'$

| Χ     | Υ     | Ζ      | _       |

|-------|-------|--------|---------|

| 0     | 0     | 0      | _       |

| 0     | 1     | 0<br>0 |         |

| 1     | 0     | 0      |         |

| 1     | 1     | 1      |         |

| Simbo | logia | _      |         |

|       |       |        | <b></b> |

#### ♦ Porta OR

$$F(X,Y)=Z=X + Y= (X + Y)'' = (X' . Y')'$$

| X          | Υ | Z |  |  |  |

|------------|---|---|--|--|--|

| 0          | 0 | 0 |  |  |  |

| 0          | 1 | 1 |  |  |  |

| 1          | 0 | 1 |  |  |  |

| 1          | 1 | 1 |  |  |  |

| Simbologia |   |   |  |  |  |

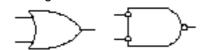

#### ♦ Porta NAND

$$F(X,Y)=Z=(X . Y)'=(X' + Y')$$

| X        | Υ     | Z |   |

|----------|-------|---|---|

| 0        | 0     | 1 |   |

| 0        | 1     | 1 |   |

| 1        | 0     | 1 |   |

| 1        | 1     | 0 |   |

| Simbo    | logia |   |   |

| $\dashv$ | _     | ` | 4 |

| 4        |       | ሥ |   |

## ♦ Porta NOR

$$F(X,Y)=Z=(X+Y)'=(X' . Y')$$

| Χ | Υ | Ζ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Simbologia

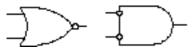

### ♦ Porta XOR (OU-EXCLUSIVO)

$$F(X,Y)=Z=(X\oplus Y)=X'Y+XY'$$

$F(X,Y)=1$  quando  $X \neq Y$

| X | Υ | Ζ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Simbologia

Teoremas:

$$X \oplus 1 = X'$$

$$X \oplus X = 0$$

$$X \oplus X' = 1$$

$$X \oplus Y = Y \oplus X$$

$$(X \oplus Y) \oplus Z = X \oplus (Y \oplus Z)$$

$$X (Y \oplus Z) = XY \oplus X Z$$

$$X \oplus Y' = (X \oplus Y)' = XY + X'Y'$$

$$X \oplus Y = X'Y + XY'$$

$$X \oplus X \oplus X = X \oplus 0 = X$$

(N° impar de termos)

$$X \oplus X \oplus X \oplus X = 0 \oplus 0 = 0$$

(N° par de termos)

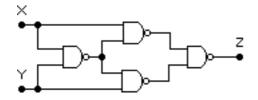

Realização de uma porta XOR com portas NAND

$$F(X,Y)=Z=X'Y+XY'=X(X'+Y')+Y(X'+Y')=(X(X'+Y')+Y(X'+Y'))''=((X(X'+Y'))''-((X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))'-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))'-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'X'+Y'))''-(X(X'Y$$

Porta XNOR (OU-EXCLUSIVO NEGADO)

$$F(X,Y)=Z=(X\oplus Y)'=X'Y'+XY$$

=  $(X\oplus Y')=(X'\oplus Y)$

$F(X,Y)=1$  quando  $X=Y$

| Χ           | Υ | Ζ |  |  |

|-------------|---|---|--|--|

| 0           | 0 | 1 |  |  |

| 0           | 1 | 0 |  |  |

| 1           | 0 | 0 |  |  |

| 1           | 1 | 1 |  |  |

| Simbologia  |   |   |  |  |

| <b>&gt;</b> |   |   |  |  |

## Exemplo de aplicação de portas XOR

$F(A,B,C)=\sum m(1,2,4,7)=A'B'C+A'BC'+AB'C'+ABC$  (forma mínima soma de produtos)

F(A,B,C) = A'B'C+A'BC'+AB'C'+ABC =A'(B'C+BC')+A(B'C'+BC)  $=A'(B\oplus C)+A((B\oplus C)')$   $=A\oplus (B\oplus C)$   $=A\oplus B\oplus C$

## Síntese de circuitos lógicos

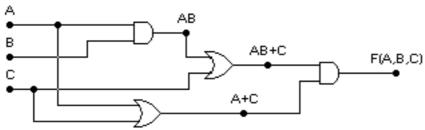

Implementação directa de funções a partir da respectiva expressão lógica

Exemplo:  $F(A,B,C)=(A+C) \cdot ((A \cdot B) + C)$ Circuito lógico correspondente

Implementação de funções com estruturas a dois níveis

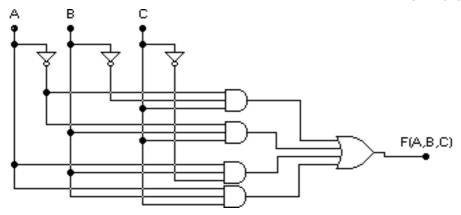

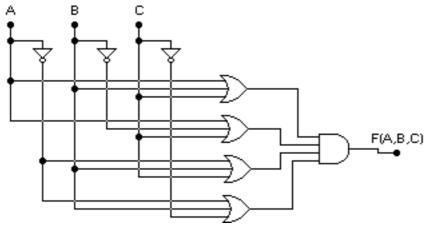

Forma canónica soma de produtos

Exemplo:

$F(A,B,C) = A'B'C+A'BC+ABC'+ABC=\sum m(1,3,6,7)$

Estrutura AND-OR

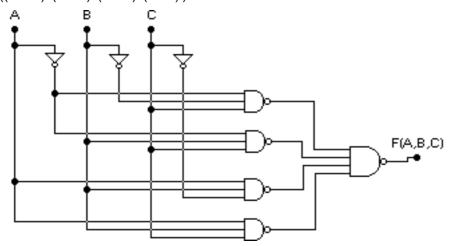

#### Estrutura NAND-NAND

Neste tipo de estrutura apenas se utilizam portas NAND. Note-se que não se consideram os inversores aplicados às variáveis de entrada.

F(A,B,C) = A'B'C + A'BC + ABC' + ABC

=( A'B'C+A'BC+ABC'+ABC)"

=((A'B'C)'.(A'BC)'.(ABC')'.(ABC)')'

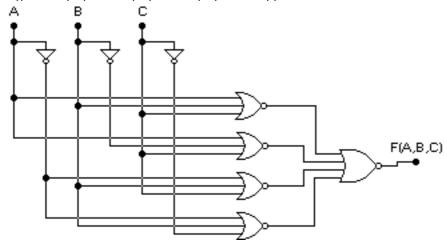

#### ♦ Forma mínima soma de produtos

F(A,B,C)= A'B'C+A'BC+ABC'+ABC = $\sum m(1,3,6,7)$ = A'C+AB Estrutura AND-OR

#### Estrutura NAND-NAND

$F(A,B,C) = A'B'C + A'BC + ABC' + ABC = \sum m(1,3,6,7) = A'C + AB = (A'C + AB)'' = ((A'C)'.(AB)')'$

#### Forma canónica produto de somas

Exemplo:

$F(A,B,C) = (A+B+C).(A+B'+C).(A'+B+C).(A'+B+C') = \prod M(0,2,4,5)$ Estrutura OR-AND

#### Estrutura NOR-NOR

Neste tipo de estrutura apenas se utilizam portas NOR. Note-se que não se consideram os inversores aplicados às variáveis de entrada.

$F(A,B,C) = (A+B+C).(A+B+C).(A'+B+C).(A'+B+C') = \prod M(0,2,4,5)$ =((A+B+C).(A+B+C).(A'+B+C'))''

=((A+B+C)'+(A+B'+C)'+(A'+B+C)'+(A'+B+C')')'

#### ♦ Forma mínima produto de somas

$F(A,B,C) = (A+B+C).(A+B+C).(A'+B+C).(A'+B+C') = \prod M(0,2,4,5) = (A+C).(A'+B)$ Estrutura OR-AND

#### Estrutura NOR-NOR

$$\begin{split} F(A,B,C) &= (A+B+C).(A+B'+C).(A'+B+C).(A'+B+C') = \prod M(0,2,4,5) = (A+C).(A'+B) \\ &= ((A+C).(A'+B))'' = ((A+C)'+(A'+B)'')' \end{split}$$

## Implementação de funções a partir da formulação verbal

#### Exemplo:

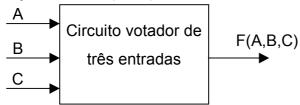

Sintetize, com portas lógicas elementares, um circuito votador de 3 entradas. Neste tipo de circuito, a saída está a zero se duas ou mais entradas estão a zero e está a um se duas ou mais entradas estão a um.

A partir da formulação verbal, obtém-se a respectiva tabela de verdade, recorrendo em seguida ao mapa de Karnaugh para a obtenção da forma mínima, a qual constitui o ponto de partida para o circuito lógico.

Diagrama de blocos

Variáveis de entrada: A,B,C Função de saída: F(A,B,C)

#### Tabela de verdade:

O preenchimento da coluna F(A,B,C) resulta da interpretação da formulação verbal.

| <br>Α | В | С | F(A,B,C) |

|-------|---|---|----------|

| 0     | 0 | 0 | 0        |

| 0     | 0 | 1 | 0        |

| 0     | 1 | 0 | 0        |

| 0     | 1 | 1 | 1        |

| 1     | 0 | 0 | 0        |

| 1     | 0 | 1 | 1        |

| 1     | 1 | 0 | 1        |

| 1     | 1 | 1 | 1        |

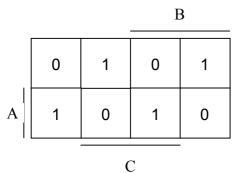

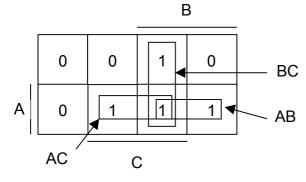

Mapa de Karnaugh

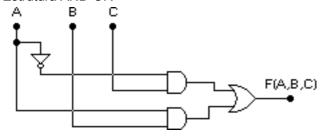

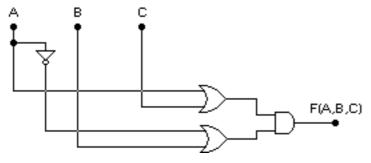

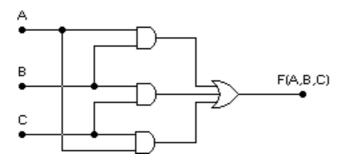

Forma mínima soma de produtos F(A,B,C)= AB+AC+BC Circuito lógico:

### Estrutura AND-OR

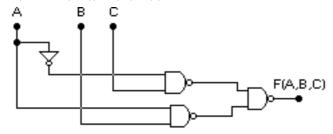

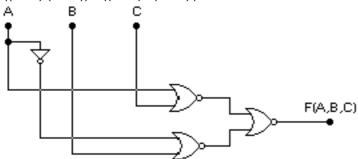

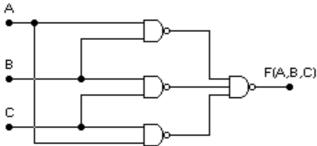

## Estrutura NAND-NAND

### Análise de circuitos lógicos

Da análise de um circuito lógico resulta uma representação alternativa das funções implementadas num circuito lógico, normalmente, recorrendo-se a expressões lógicas ou tabelas de verdade.

#### Exemplo:

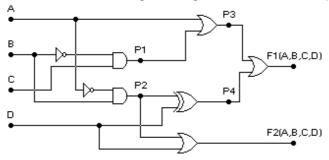

Dado o circuito lógico da figura, determinar as expressões lógicas de F1e F2.

Definem-se os pontos intermédios:

P1=B'C

P2=A'B

P3=A+P1=A+B'C

P4=P2⊕D=A'BD'+(A'B)'D=A'BD'+(A+B')D

=A'BD'+AD+B'D

F1=P3+P4=A+B'C+A'BD'+AD+B'D

=A(1+D)+B'C+A'BD'+B'D

=A+B'C+A'BD'+B'D

=A+BD'+B'D+B'C

F2=P2+D=A'B+D

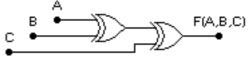

Exemplo:

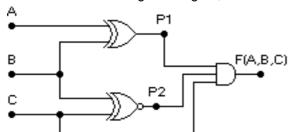

Dado o circuito lógico da figura, determinar a tabela de verdade de F.

Definem-se os pontos intermédios:

P1=A⊕B

P2=(B⊕C)'

F(A,B,C)=P1.P2.C

Tabela de verdade

| Α | В | С | P1  | P2     | F(A,B,C) |

|---|---|---|-----|--------|----------|

|   |   |   | A⊕B | (B⊕C)' | P1.P2.C  |

| 0 | 0 | 0 | 0   | 1      | 0        |

| 0 | 0 | 1 | 0   | 0      | 0        |

| 0 | 1 | 0 | 1   | 0      | 0        |

| 0 | 1 | 1 | 1   | 1      | 1        |

| 1 | 0 | 0 | 1   | 1      | 0        |

| 1 | 0 | 1 | 1   | 0      | 0        |

| 1 | 1 | 0 | 0   | 0      | 0        |

| 1 | 1 | 1 | 0   | 1      | 0        |

$F(A,B,C)=m_3=A'BC$

O mesmo resultado pode ser obtido por manipulação algébrica, considerando:

$F(A,B,C)=(A \oplus B) \cdot (B \oplus C)' \cdot C$

=(AB'+A'B).(BC+B'C').C

=(AB'BC+AB'B'C'+A'BBC+A'BB'C').C

=(0+AB'C'+A'BC+0).C

=(AB'C'+A'BC).C

=(AB'C'C+A'BCC)

=À'BC

O mesmo resultado pode ser obtido por interpretação/leitura da expressão lógica da função, considerando:

$F(A,B,C)=(A\oplus B) \cdot (B\oplus C)' \cdot C$

Sendo a expressão um produto, então

F(A,B,C)=1 quando

C=1 e (B⊕C)'=1 e (A⊕B)=1

⇔C=1 e (B=C) e (A≠B)

⇔C=1 e B=C=1 e A≠B

⇔C=1 e B=C=1 e A=0

a que corresponde o mintermo m<sub>3</sub>, logo F(A,B,C)=A'BC